# A Ka-Band CMOS Beamforming Front-End IC for RF Inter Satellite Link System

Jinseok Park

Satellite Payload Research Section

ETRI

Daejeon, South Korea

jinseok131@etri.re.kr

Soonyoung Hong

Satellite Payload Research Section

ETRI

Daejeon, South Korea

scottie\_hong@etri.re.kr

Seong-Mo Moon

Satellite Payload Research Section

ETRI

Daejeon, South Korea

smmoon@etri.re.kr

Dongpil Chang Satellite Payload Research Section ETRI Daejeon, South Korea dpjang@etri.re.kr Junhan Lim

Satellite Payload Research Section

ETRI

Daejeon, South Korea

flawnsgks@etri.re.kr

Byung-Sun Lee Satellite Payload Research Section ETRI Daejeon, South Korea lbs@etri.re.kr

Abstract—A Ka-band CMOS 1-channel beamforming frontend IC for RF inter-satellite link system is presented. In particular, variable gain phase shifters (VGPS) and PA linearizer are integrated. The VGPS has an orthogonal phase and gain control function, which reduces chip size and power consumption. The PA linearizer reduces both AM-AM and AM-PM distortions of the PA, which improves linear output power. The 1-channel beamforming front-end IC has 6-bit phase and 6-bit gain control resolutions with TX OP<sub>1dB</sub> of 18.5 dBm.

Keywords—beamforming, CMOS, linearizer, orthogonal phase and gain control, phase shifter, receiver, transmitter

### I. INTRODUCTION

Beamforming technology is one of the key technologies for RF inter-satellite link systems. In particular, CMOS-based beamforming front-end ICs are receiving much attention due to their high level of integration and low cost [1]-[9]. However, CMOS PA has poor linearity and efficiency. Since the conventional digital pre-distortion is not easy to be applied to the phased array system [8], an analog PA linearizer must be integrated. Also, the conventional phase and gain control blocks have high phase and gain errors with large chip sizes. To solve these issues, a 1-channel CMOS beamforming frontend IC including PA linearizer and variable gain phase shifter (VGPS) with lower phase and gain error is proposed.

## II. PROPOSED BEAMFORMING FRONT-END IC

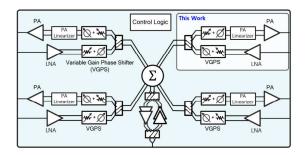

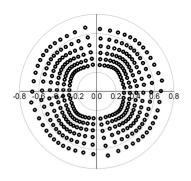

Fig. 1 shows the block diagram of the beamforming frontend IC. Each channel contains PA, PA linearizer, VGPS, T/RX switch, and LNA. All differential structures is adapted to reduce the parasitic ground inductance effect. A VGPS based on [10] is used for phase and gain control. To improve phase/gain control speed, short gate length transistors are used for the phase/gain control DAC. Fig. 2 shows the simulated static vector constellations of the 1-channel front-end IC. It can cover 360° with low gain errors.

The PA linearizer in [8], [12] improves both AM-AM and AM-PM distortion of the PA. However, its improvement in AM-PM distortion is very limited. Also, the linearizers lower the efficiency of the PA. To solve this issue, a two-stack Cold-FET-based linearized is proposed and connected to the input of the CS amplifier. Thanks to the proposed structure, AM-PM distortion is reduced and efficiency degradation due to the linearizer is minimized.

Fig. 1. Block diagram of the RF beamforming front-end IC.

Fig. 2. Simulated static vector constellations of the 1 channel front-end IC at 26 GHz.

A differential SPDT structure with alternating NMOS and PMOS structure [11] is used for the T/RX switch to have high power handling capability with low insertion loss.

## III. IMPLEMENTATION AND MEASUREMENT RESULTS

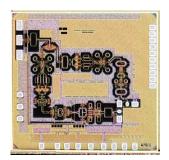

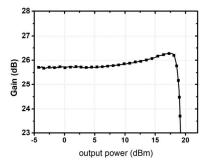

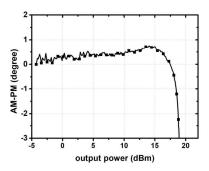

The proposed 1-channel beamforming front-end IC was fabricated using a 65-nm RF CMOS process. Fig. 3 shows a chip photo of the implemented 1-channel beamforming front-end IC. The IC was measured using on-wafer probing. Fig. 4 shows measured gain with respect to output power. Thanks to the analog linearizer, the gain is expanded in the high power region, which improves AM-AM distortion of the PA. OP<sub>1dB</sub> of 18.5 dBm is achieved with the linearizer. Compared to that of the PA without the linearizer, OP<sub>1dB</sub> of ~2.5 dB is improved. Fig. 5 shows a measured AM-PM distortion of the 1-channel IC. Thanks to the analog linearizer, the phase is lagged in the

Fig. 3. Chip photo of the 1-channel beamforming front-end IC.

Fig. 4. Measured gain of the 1-channel beamforming front-end IC with respect to output power.

Fig. 5. Measured AM-PM distortion of the 1-channel beamforming front-end IC.

mid-power region and is led in the high-power region. The measured AM-PM distortion until  $OP_{1dB}$  was less than  $1.5\,^\circ$  . Compared to that of the PA without the linearizer, AM-PM distortion of about  $3\,^\circ$  is reduced. The RMS phase error was lower than  $1.5\,^\circ$  at 27~GHz.

# IV. CONCLUSION

A Ka-band CMOS 1-channel beamforming front-end IC for RF inter-satellite link system was presented. The VGPS with an orthogonal phase and gain control function reduced chip size and power consumption. The Cold-FET-based linearizer reduced both AM-AM and AM-PM distortions of the PA with minimal efficiency degradation. Table I shows the performance comparison with recently reported Ka-band Si-based beamforming front-end ICs. The proposed 1-channel IC achieved the highest OP<sub>1dB</sub> and the lowest RMS phase and

gain errors. It also has comparable NF and phase/gain control resolution.

TABLE I. PERFORMANCE COMPARISON WITH RECENTLY REPORTED KA-BAND BEAMFORMING ICS

| Parameter                                      | This Work                                    | JSSC17 [5]                                                | Tokyo Tech.<br>ISSCC 19 [6]        | LG<br>JSSC18 [3]               | Qualcomm<br>ISSCC18 [13] | UCSD<br>JSSC18[1]                                      |

|------------------------------------------------|----------------------------------------------|-----------------------------------------------------------|------------------------------------|--------------------------------|--------------------------|--------------------------------------------------------|

| Process                                        | 65 nm<br>Bulk CMOS                           | 130 nm<br>SiGe BiOMOS                                     | 65 nm<br>Bulk CMOS                 | 28 nm LP<br>CMOS               | 28 nm LP<br>RF CMOS      | 180 nm<br>SiGe BICMOS                                  |

| Tx OP1dB (dBm)                                 | 18.5                                         | 13.5                                                      | 11.3                               | 9.5                            | 12                       | 10.5                                                   |

| Phase/Gain Control<br>Resolution (bit)         | 6/6                                          | 5/5                                                       | 21                                 | 3/-                            | 3/3                      | 6/4                                                    |

| RMS Phase Error by<br>Phase & Gain Control (*) | <2<br>(Phase & gain<br>simultaneous control) | 8**<br>(gain control only)<br>1.5<br>(phase control only) | - / 1.8<br>(phase control<br>only) | -/7<br>(phase control<br>only) | -1                       | 6**<br>(gain control only)<br>5<br>(phase control only |

| RMS Gain Error (dB)                            | < 0.2                                        | 1.4**                                                     | 0.4                                | -                              | - 4                      | 0.9                                                    |

| Noise Figure (dB)                              | <4***                                        | 6                                                         | 4.2                                | 6.7                            | 3.8 *                    | 4.6                                                    |

<sup>\*</sup> Estimated from the paper, \*\* Peak error, \*\*\*Simulation Result

#### ACKNOWLEDGEMENT

This work was supported by Institute for Information & communications Technology Planning and Evaluation (IITP) grant funded by the Korea government (MSIT) (No.2018-0-00190, Development of Core Technology for Satellite Payload)

#### REFERENCES

- [1] K. Kibaroglu *et al.*, "A Low-Cost Scalable 32-Element 28-GHz Phased Array Transceiver for 5G Communication Links Based on a 2 x 2 Beamformer Flip-Chip Unit Cell," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1260-1274, May 2018.

- [2] J. Pang et al., "A CMOS Dual-Polarized Phased-Array Beamformer Utilizing Cross-Polarization Leakage Cancellation for 5G MIMO Systems," in *IEEE Journal of Solid-State Circuits*, vol. 56, no. 4, pp. 1310-1326, April 2021.

- [3] H. Kim et al., "A 28-GHz CMOS Direct Conversion Transceiver with Packaged 2 x 4 Antenna Array for 5G Cellular System," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1245-1259, May 2018.

[4] A. Natarajan, A. Komijani and A. Hajimiri, "A fully integrated 24-GHz

- [4] A. Natarajan, A. Komijani and A. Hajimiri, "A fully integrated 24-GHz phased-array transmitter in CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2502-2514, Dec. 2005.

- [5] B. Sadhu et al., "A 28-GHz 32-Element TRX Phased-Array IC with Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3373-3391, Dec. 2017.

- 6] J. Pang et al., "21.1 A 28GHz CMOS Phased-Array Beamformer Utilizing Neutralized Bi-Directional Technique Supporting Dual-Polarized MIMO for 5G NR," 2019 IEEE International Solid-State Circuits Conference - (ISSCC), 2019, pp. 344-346.

- [7] J. Pang et al., "A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1228–1242, May 2019.

- [8] J. Park et al., "Design of a Ka-Band Cascode Power Amplifier Linearized With Cold-FET Inter-Stage Matching Network" in IEEE Transactions on Microwave Theory and Techniques, vol. 69, no. 2, pp. 1429-1438, Feb. 2021.

- [9] S. Shakib et al., "A Highly Efficient and Linear Power Amplifier for 28-GHz 5G Phased Array Radios in 28-nm CMOS", IEEE J. Solid-State Circuits, vol. 51, no. 12, pp. 3020-3036, Dec. 2016.

- [10] J. Park et al., "A 28GHz 20.3%-Transmitter-Efficiency 1.5°-Phase-Error Beamforming Front-End IC with Embedded Switches and Dual-Vector Variable-Gain Phase Shifters," IEEE International Solid-State Circuits Conference (ISSCC) Dig. Tech. Paper, pp. 176-178, Feb 2019.

- [11] J. Park et al., "A Small-Size K-Band SPDT Switch Using Alternate CMOS Structure With Resonating Inductor Matching," in *IEEE Microwave and Wireless Components Letters*, vol. 30, no. 11, pp. 1093-1096, Nov. 2020.

- [12] G. Cho et al., "A 25.5-dB Peak Gain F-Band Power Amplifier with an Adaptive Built-In Linearizer," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 1, pp. 106-108, Jan. 2020.

[13] J. D. Dunworth *et al.*, "A 28 GHz bulk-CMOS dual-polarization phased array transceiver with 24 channels for 5G user and basestation

equipment," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2018, pp. 70–72.